Was ist das "Virtual-Date-Lab"

Das Virtual-Date-Lab wurde entwickelt, um Studierenden der Universität Paderborn die Möglichkeit zu geben, die Hardwarebeschreibungssprache VHDL zu erlernen. Mit Hilfe von VHDL können Schaltungen auf einem Field Programmable Gate Array (FPGA) implementiert werden. Dies dient u.a. zur Veranschaulichung und Vertiefung der Vorlesungsinhalte der Veranstaltung Digitaltechnik.

Da für die Entwicklung speicherintensive Software sowie ein Entwicklungsboard benötigt wird, ist es normalerweise nicht so einfach möglich, zu Hause damit zu beginnen. Das Virtual-Date-Lab stellt die Software per Remote Desktop zur Verfügung und das Verhalten des Entwicklungsboards bzw. der Hardware kann dann mit Hilfe eines Live Videostreams beobachtet werden.

Das zugrundeliegende Betriebssystem ist Debian 11 (Bullseye). Die Entwicklungsumgebung für VHDL ist Vivado 2022.2 der Firma Xilinx. Als Entwicklungsboard kommt des Nexys4 DDR Board von der Firma Digilent zum Einsatz.

Voraussetzungen

Für den Zugriff auf das virtuelle Labor sind folgende Voraussetungen zwingend notwendig:

- aktiver IMT Account an der Universität Paderborn

- Folgende Dienste müssen im Serviceportal der Universität Paderborn aktiviert sein:

- Basisdienste: Uni-Account, Netzwerkzugang

- Zentrum für Informations- und Medientechnologien (IMT): Netzwerkspeicher

- Rechnerzugang und Poolräume: Rechnerzugang Datentechnik (DATE) Hinweis: Dieser Dienst wird manuell genehmigt, wodurch es zu Verzögerungen kommen kann.

- VPN Zugang zum Netzwerk der Universität Paderborn (Anleitung)

- aktive Teilnahme im Panda Kurs der jeweiligen Veranstaltung (z.B. SS23 - L.079.05200 Digitaltechnik)

- aktueller Browser (getestet wurden Firefox und Chrome)

Anmeldung

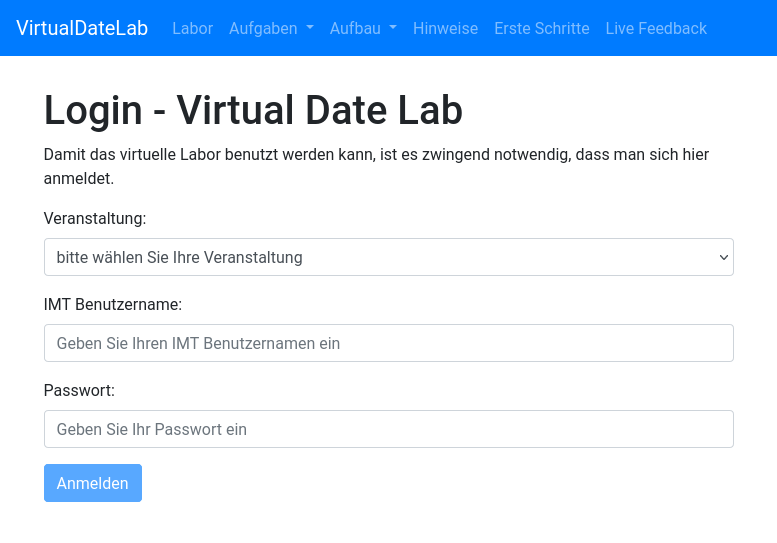

Sind alle obigen Vorasussetzungen erfüllt, müssen Sie sich zunächst [hier] anmelden. Wählen sie dazu den jeweiligen Panda Kurs aus und geben Sie Ihr IMT Benutzernamen und das IMT Passwort ein.

Je nachdem, wie die Kurse konfiguriert sind, haben sie jetzt meherere Möglichkeiten:

- Kurskonfiguration mit Terminbuchung

- Kurskonfiguration mit Panda Grupen